MIPS proAptiv是微处理器IP核系列,旨在提供互联消费电子产品(包括互联电视和机顶盒)以及嵌入式应用中的高性能计算所需的出色的顶级性能。

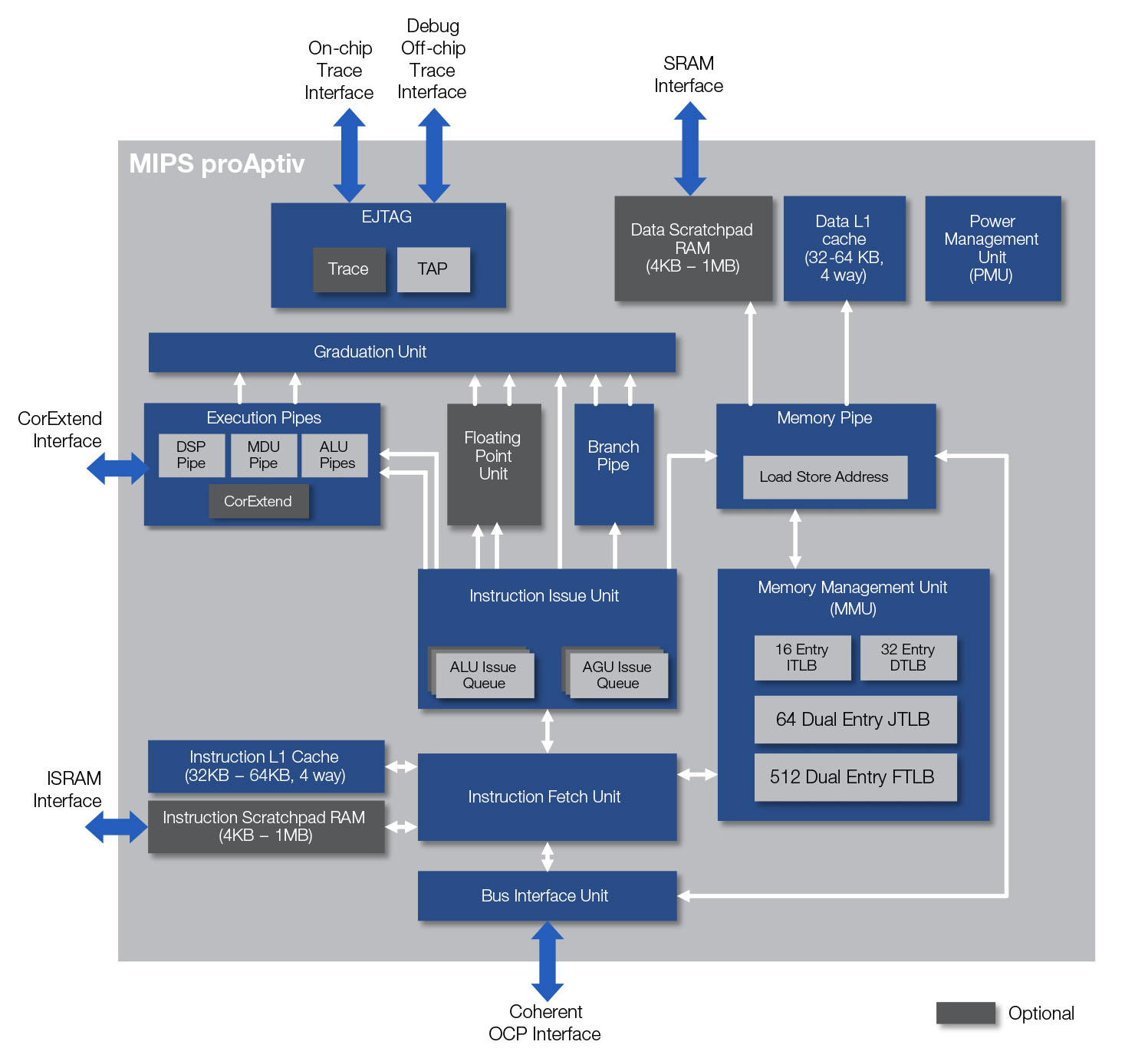

proAptiv CPU基于MIPS32架构的广泛问题,深度乱序(OoO)的实现,并提供支持多达六个内核的单核和多核产品版本。

proAptiv系列利用先进的微架构,升级的浮点单元(FPU)和增强的多核互连,在性能上实现了跨越上一代MIPS Classic CPU IP核的重大飞跃,同时相比于同一工艺节点中仅需其他竞争内核将近一半的面积大小。

特点

• 具有多达六个内核的32位MIPS32®Release 3指令集架构

• 高性能,16阶段,多发射乱序(OoO)管道

• I / D L1高速缓存大小分别为32KB或64KB,4路组关联

• 可编程内存管理单元 (MMU)

• MIPS DSP 模块, version 2

• 可选的第二代高性能双发行浮点单元 (FPU)

• 基本核心和多核心集群级别的高级电源管理

• EJTAG/PDtrace 调试

优势

• 超标量OoO处理器,具有针对应用程序优化的单核和多核版本

• 复杂的分支预测,可实现现代软件工作负载的性能

• 加载/存储绑定以获得最佳数据移动性能

• EVA(增强型虚拟寻址)–可编程虚拟地址映射,可最佳利用32位地址空间

• 行业领先的基准和真实世界的性能,而面积和功率却没有增加

• 广泛的软件和生态系统支持以及成熟的工具链

• 可用作可综合IP,可在带有标准单元和存储器的任何工艺节点中实施

应用

• 连接的DTV / STB

• 联网

• 汽车信息娱乐

• 高性能计算

基准规格

| 目标规格 |

TSMC 28HPM |

| 频率 |

1 GHz - 2+ GHz* |

| CoreMark/MHz (每核) |

5.1 |

| Total CoreMark @ 1.5 GHz |

> 7500 每核 |

| DMIPS/MHz (每核) |

3.5 |

| Total DMIPS @ 1.5 GHz |

> 5250 每核 |

注意:所示频率是针对完全平面规划的双核实现的,范围从最坏情况下的12T SVt面积优化的硅角到典型的12T MVt速度优化的typical corner。

每个基本内核配置:

• 具有奇偶校验,BIST的32KB Data / Inst L1高速缓存

• 新型高速 FPU

• 功能齐全的MMU,使用多层TLB(I / D uTLB + 128个条目VTLB + 1024个条目FTLB)

• PDtrace™ 调试

多核集群配置:

• 每个以上具有两个完全配置的proAptiv内核

• Coherence Manager +集成1MB L2 $ w / ECC

• 1个硬件IO一致性单元(IOCU)端口

集群级别的PDtrace实现库/参数–基于以下方面进行了速度优化:

• 台积电28HPM 12T标准单元+ Synopsys存储器

• 数据量测是在最坏的操作条件情况slow-corner硅片(零温度,WCZ),OCV为10%,时钟抖动裕度为25ps ,而非在typical硅片上

文件