MIPS P6600是一个64位处理器内核,代表了MIPS P类家族高阶CPU的发展。

P6600建立在32位 P5600 CPU之上,并为下一代高性能64位MIPS处理器铺平了道路,是最高效的主流高性能CPU选择,可为功能强大的多核64位SoC提供最佳的区域效率, 在家庭娱乐,网络,汽车,嵌入式高性能计算等领域的应用。

MIPS P6600 CPU基于广泛使用的问题,利用MIPS64 架构的最新版本6深度乱序(OoO)实作,在单个群集中最多支持六个内核,并具有高性能的缓存一致性。 作为这种原始功能的补充,该内核包括128位整数和浮点SIMD处理,硬件虚拟化以及MIPS64架构带来的更大的实体和虚拟寻址空间。

与领先的IP内核替代产品相比,P6600处理器可在更小的芯片尺寸内提供性能。 SoC设计人员可以利用这种效率优势来节省成本,或者实现其他内核以提供与竞争性芯片相比所具有的性能优势。

P6600 优势

• MIPS64 r6 架构– 提供了更大的虚拟和物理寻址,以及在64位操作和数据移动方面的更高性能。利用MIPS64的最新版本6,并针对运行JIT,Javascript,浏览器,PIC等进行了优化。

• 128-bit SIMD – 加速了音频,视频,图形,图像,语音和其他面向DSP的软件算法的执行,其指令集设计用于以C,OpenCL等高级语言进行开发

• 基于硬件虚拟化的MIPS多域安全技术–确保需要安全保护的应用程序彼此有效,可靠地隔离,并免受非安全应用程序的攻击

• 用于企业/消费者分区,安全内容访问,付款/交易以及将安全方案与众多内容源隔离的多上下文安全平台

• 复杂的分支预测,可在深度流水线CPU上最大化利用率和性能

• 加载/存储绑定以获得最佳数据搬移性能

• 广泛的软件和生态系统支持以及成熟的工具链

• 可用作可在任何工艺节点中实现的可综合IP,带有标准单元和存储器

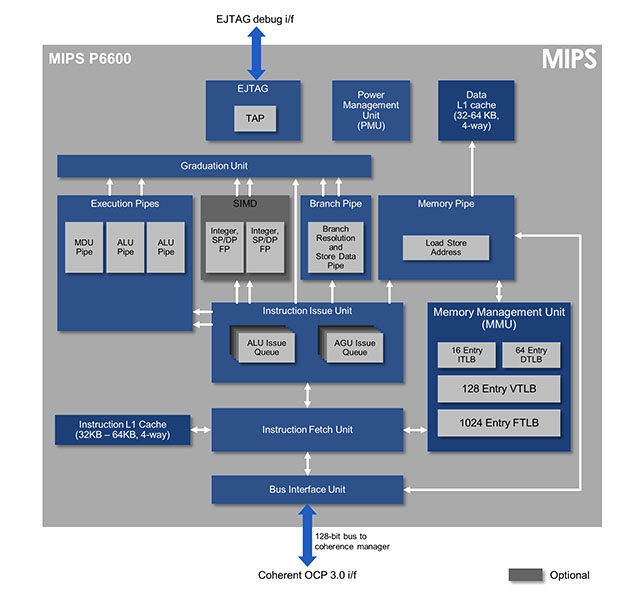

基本核心功能

• 64位MIPS64®版本6指令集架构

• 高性能,16阶段,广泛发射的乱序(OoO)管道

º每个周期提取四指令

º每个周期三重绑定派发

º每周期4个整数和2个SIMD操作的指令峰值发射

º复杂的分支预测方案,再加上L0 / L1 / L2分支目标缓冲区(BTB),返回预测堆栈(RPS),跳转寄存器高速缓存(JRC)

º指令绑定–将两个32位整数访问合并为一个64位访问,或将两个64位浮点访问合并为一个128位访问,从而使内存密集型数据移动例程最多增加2倍

• 指令和数据的L1高速缓存大小分别为32KB或64KB,4路组关联

• 新的高性能双发射128位SIMD单元-可选

º2 x 128位寄存器组,向SIMD单元加载/从SIMD单元加载/存储128位

º本机数据类型:

• 8/16/32位整数和定点,16/32/64位浮点

º符合IEEE-754 2008

º通过CPU内核全速运行

• 全面的硬件虚拟化

º提供内核和用户空间的root和guest虚拟机特权级别

º支持多个来宾,每个来宾具有完整的虚拟CPU =来宾OS保持不变

º单独的TLB,root和guest虚拟机的COP0上下文–>完全隔离,快速上下文切换,由root处理异常和中断

ºTLB中的HW表格伴随支持可实现最佳性能

º完整的SoC虚拟化支持(IOMMU和中断处理–请参阅多核功能)

• 可编程内存管理单元 (MMU)

º增强型虚拟地址(EVA)-可编程内核和用户段大小

º扩展实体地址(XPA)–提供扩展到40位物理地址位(1 TB)

º第一级微型TLB(uTLB)– 16个输入指令TLB,32个输入数据TLB

º2级TLB –同时访问,可变和固定页面大小

• 64x2入口VTLB,512x2入口4路组关联FTLB

º硬件表格伴随,可快速填充页面

• 电源管理功能

º多核集群电源控制器 (CPC):

• 基于寄存器,对操作系统可见/可控制

• 每个CPU电压域门控; 每个CPU时钟门控

• 集群级DVFS功能

º内核水平

• 整个内核的粗细和细粒度时钟门控

• 数据和指令L1缓存的路途预测

• 基于指令和寄存器的睡眠模式

• EJTAG / PDtrace调试块和接口

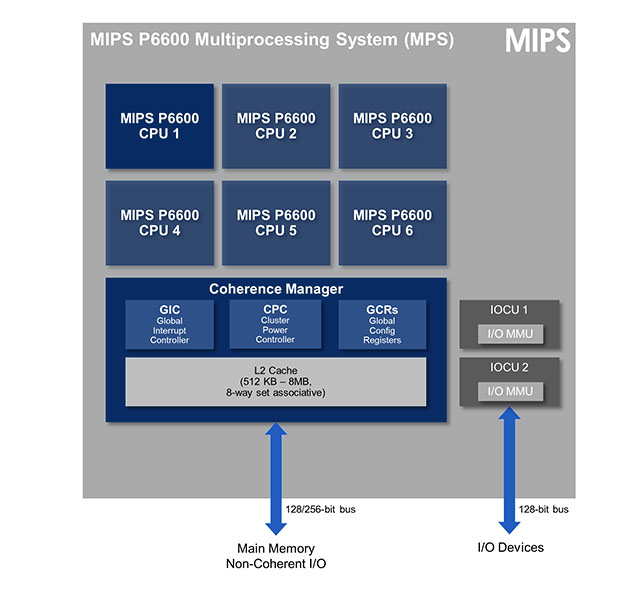

º干多核处理器功能

• 超标量,深度OoO多核处理器

• 完整的多核系统,旨在获得最大的群集级带宽

º一致性控制器 – 在一个集群中最多支持六个核心的多核心配置

º高带宽256位内部数据路径和外部系统接口

º集成的L2缓存(L2 $):4路集关联,最大8MB内存

• L2 $ RAM上的ECC选项可提供更高的数据可靠性

• 可配置的等待状态到RAM以实现最佳的L2 $设计

• L2 $硬件预取,可实现更高的吞吐量和性能

º每个相干处理系统最多两个IO相干单元(IOCU

º集群电源控制器(CPC),用于每个CPU的电压/时钟门控

º256中断全局中断控制器 (GIC)

º系统级别的虚拟化支持– IOCU具有IO MMU,而GIC具有虚拟化中断

规格

| 目标 |

TSMC 28HPM |

| 频率 |

1 GHz – 2+ GHz* |

| CoreMark/MHz (每核) |

> 5 |

| Total CoreMark @ 1.5GHz |

> 7500 每核 |

| DMIPS/MHz (每核) |

3.5 |

| Total DMIPS @ 1.5GHz |

> 5250 每核 |

注意:指示的频率范围从最坏情况下的12T SVt面积优化的硅角,到12T MVt速度优化的典型角硅。 最终生产RTL结果可能会有所不同。

每个基本内核配置:

• 具有奇偶校验,BIST的32KB Data / Inst L1高速缓存

• 新型高速整数+浮点(SP和DP)SIMD单元

• 功能齐全的MMU,使用多层TLB(I / D uTLB + 128个条目VTLB + 1024个条目FTLB)

多核集群配置:

• 每个以上具有两个完全配置的P6600内核

• Coherence Manager + 集成1MB L2 $ w / ECC

• 1个硬件IO一致性单元(IOCU)端口

实施库/参数–基于以下方面进行了速度优化:

• 台积电28HPM 12T标准单元+ Synopsys存储器

• 数据量测是在最坏的操作条件情况slow-corner硅片(零温度,WCZ),OCV为8%,时钟抖动裕度为25ps,而非在typical硅片上

文件