MIPS I6500多处理器内核基于多年淬炼的MIPS64® 架构,扩展成多样的可许可内核种类并提高其可扩展性,为异构计算提供了引人注目的解决方案。

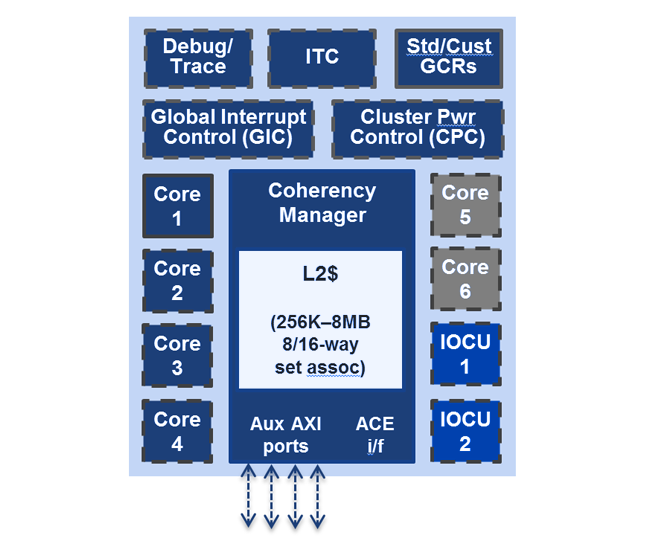

该IP内核产品强调的关键功能是“异构的内与外”,许多内核/多群集的可扩展处理以及实时决定性执行(即透过利用其对硬件虚拟化的支持)也使I6500系列强大的IP内核成为业界灵活且最具扩展性的产品之一 。

I6500的灵活性和可扩展性使其成为异构计算此类应用不断增长和变化需求的理想选择,这些应用包括无人机,工业自动化,高性能网络,高级驾驶员辅助系统(ADAS)和自动驾驶,机器学习,安全性和视频分析。

此外MIPS I6500-F 内核版本是基于I6500更增加了功能安全方面的附加功能。

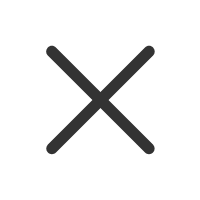

I6500系列一如I6400 内核系列,其基础建立在多线程超标量设计的CPU内核,在一个多核群集中,它最多可以支持配置六个内核。可以将集群中的每个内核分别配置,作为其“异构内部”功能的基础,并进行优化和调整以符合整个解决方案所需的性能,功耗和面积要求,切适应用需求。 这包括改变例如,每个L1缓存的大小,硬件线程的数量,调试器弹性的配置以及可选配的功能包含SIMD / FPU处理单元,还有每个内核的Data ScratchPad RAM(SPRAM),多达四个用于低延迟外设或群集级SPRAM的AXI端口以及线程间通信(ITC)支持。 这些功能支持嵌入式系统中的确定性,低延迟操作和快速路径消息传递,以及高性能网络/数据处理应用程序的实现,可作为标准缓存存储系统的辅助。

I6500处理器中的同时多线程与硬件虚拟化相结合,使多个执行环境可以彼此隔离地同时运行,且因内文切换所产生的虚耗为零。

每个CPU的工作频率和电压也可以变化,从而实现性能和功耗的动态运行时优化,甚至可以针对单个集群中不同的性能,面积和功耗属性对内核进行硅设计优化。 在上图中可以看到这种配置的示例以及上述某些功能。

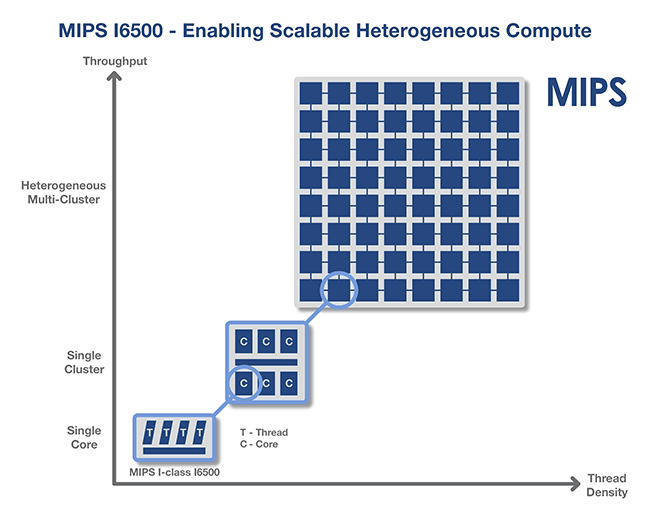

I6500系列的主要功能之一是对多群集和“异构外部”计算可扩展性的支持。I6500群集的主要系统接口与ACE兼容。 因此,能与第三方SoC相干互连/结构替代方案一起使用,I6500系列可用于多达64个集群或大于1500个处理元素的“许多内核”实现更复杂的一致性多群集系统(多达四个线程/核,最多六个内核/群集,最多64个群集)。 MIPS还提供了多群集子系统,作为扩展许可选项之一。

I6500系列的“异构外部”功能包括混合该技术基础的多群集CPU功能的功能,并增加了与其他处理/计算元素协同工作的功能。 这包括使用ACE兼容协处理器支持相干多处理的能力。

I6500系列的功能通过支持构建“仅有加速器”集群的独特功能,在“异构外部”框架上进一步扩展。 实际上,可以将I6500系列平台的单个群集配置为将多达八个IO一致性单元(IOCU)连接在一起,而群集中并不生成CPU。

定制设计的或第三方的功能加速器可以通过标准的AXI4接口连接到这些IOCU端口,从而为特定任务或应用程序提供非常本地化和集中的计算资源。 这样的配置通过利用加速器单元之间的本地共享低延迟L2缓存为功能加速器集群提供了好处。 它将加速器和CPU的处理和流量集中到单独的集群中。

这样,对于每个处理群集,分配给各个L2高速缓存存储器的竞争流量和带宽分配就更少了,同时保持了各个L2高速缓存之间的存储器一致性。 与在一致的NoC架构上进一步实现加速器相比,此功能不仅提供了用于创建加速器集群的基于标准的机制,而且还提供了与CPU的本地化,更低延迟的通信。

MIPS I-类 I6500系列的主要功能/优点:

• 异构内部:在单个集群中,设计人员可以通过使用不同的线程组合,不同的缓存大小,不同的频率甚至不同的电压水平配置每个CPU来优化功耗。

• 异构外部:具有AMBA®ACE接口的最新MIPS Coherence Manager与流行的ACE相干结构解决方案(如Arteris和Netspeed的解决方案)使设计人员可以混合使用处理集群(包括PowerVR GPU)的芯片配置,以提高系统效率。

• 同步多线程(SMT):基于跨几代MIPS-CPU实现的超标量双发射设计,此行之有效的功能可在每个时钟周期执行来自多个线程的多条指令,从而提高利用率和CPU效率。

• 硬件虚拟化(VZ):I6500建立在MIPS-I6400内核首创的实时硬件虚拟化功能的基础上。设计人员可以通过安全可靠地将多个CPU内核与一个内核合并来节省成本,在需要多个内核的地方节省功率,并为每个应用程序动态确定地分配CPU带宽。

• SMT + VZ: I6500中SMT与VZ的结合为需要实时响应的应用提供了“零内文切换”。该功能以及暂存器的提供使I6500非常适合需要决定性代码执行的应用。

• 高可信度:跨其处理系列使用的MIPS多域安全技术可在可信环境中隔离应用程序,从而通过分离为安全性奠定了基础。

• 计算密集型,数据处理和网络应用程序的理想选择:I6500专为将高性能/高效数据传输到本地计算资源而设计,每个CPU具有数据暂存器,并具有在线程和内核之间快速路径消息/数据传递的功能。

• 方便易於使用的软件开发:I6500基于成熟的MIPS ISA,在多个供应商的开发生态系统中得到广泛支持。 采用I6500的客户可以享受广泛的编译器,调试器,操作系统,系统管理程序和应用程序软件的所有选择,这些编译器,调试器,操作系统,虚拟机管理程序和应用程序软件均针对MIPS ISA进行了优化。

MIPS I-类 I6500 基本内核功能

• 64位MIPS64版本6指令集架构

º 经过验证,成功且得到良好支持的64位架构

º MIPS32的超集–直接运行MIPS32软件

• 带有 同步多线程(SMT)的平衡的9阶段双发射管道

º 每个周期在单个线程或两个线程上同时执行超标量

º 每个核心最多4个线程

º 指令绑定–将连续的整数或浮点加载或存储合并到一个操作中,从而提高内存密集型数据搬移代码最多增加2倍

• 高性能双发射FPU / SIMD单元-可选

º 32 x 128位寄存器组,向SIMD单元加载或从SIMD单元存储128位

º 本机数据类型:

• 8/16/32/64位整数和定点,16/32/64位浮点

º 符合IEEE-754 2008

• 全面的硬件虚拟化

º 提供内核和用户空间的root和guest虚拟机特权级别

º 支持多个来宾,每个来宾具有完整的虚拟CPU等同来宾OS无需修改即可运行

º 单独的TLB,root和guest虚拟机的COP0内文,提供完全隔离,快速内文切换,由root处理异常和中断

º 完整的SoC虚拟化支持(IOMMU和中断处理–请参阅多核功能)

• L1 快取

º 具有ECC,4路组关联的32KB或64KB的指令和数据

• 数据暂存器RAM(D-SPRAM)

º 具有ECC的最大1 MB,用于确定性的低延迟访问和/或高性能的数据处理以及将其移出标准高速缓存存储器层次结构(例如,直接将DMA直接移入内核的本地D-SPRAM)

• 可编程内存管理单元(MMU)

º 具有阵列的第一级和第二级TLB,支持可变和固定页面大小

MIPS I-类 I6500 系列多核和多集群功能

• 一致的多核和多集群平台,提供可扩展的实现,以支持同构和异构计算应用程序

º 内核和输入/输出一致性单元(IOCU)端口混合的灵活性可实现计算和吞吐量优化,从而为应用程序需求提供更好的异构性能

º 支持多达64个计算集群的多集群实施

º IP可重覆使用:

• 可交付的单群集IP与一致性结构替代方案(与ACE兼容)结合使用,以实现多群集可扩展性,或

• 完整的多集群子系统可交付产品

• 每个集群的多核系统旨在实现最大的集群级带宽

º 一致性管理器 (CMv3.5)

• 可扩展到一致的多集群实施

• 在单个群集中,最多支持以下多端口配置:

• 单个群集中的六个核心(加上最多两个硬件I/O一致性单元)IOCU端口,或

• 八个IOCU端口,用于“群集”硬件加速器(即使在同一群集中没有CPU内核)

• 新的基于目录法的一致性方案–改善了功耗,性能和可伸缩性

• 高带宽256位内部数据路径和外部系统接口

º 集成的L2缓存(L2 $):16路集关联,最大8MB内存

• 双管道可最大化L1 $未命中的带宽

• L2 $ RAM上的ECC选项可提供更高的数据可靠性

• 可配置的等待状态到RAM以实现最佳的L2 $设计

• L2 $硬件预取,可实现更高的吞吐量和性能

º 多达四个辅助AXI端口提供启用功能,例如:

• 非一致性内存事务的单独路径

• 共享对低延迟外设的访问

• 共享对低延迟和确定性SPRAM的访问(在集群内,甚至跨集群)

º 线程间通信 (ITC)

• 核心或群集中线程之间传递消息/数据的快速路径,更高效率的替代方案

º 全域中断控制器(GIC),每个集群256个中断

º 先进的电源管理

• 内核级DVFS(动态电压和频率缩放调整)–每个内核可在独立的时钟和电压级下运行

º 系统和SoC级别的虚拟化支持

• 每个集群最多31个来宾执行环境

• IOCU包括I / O MMU; GIC具有虚拟中断

• 在系统界面给定访客ID ,用于集成到多集群和虚拟化SoC设计中

• 先进的调试功能–调试和跟踪

º 调试单元(DBU)支持JTAG或APB界面,以实现Coresight™兼容性

º 程序和数据跟踪(PDtrace™),带有片上或片外跟踪缓冲

文件