MIPS P5600具有业界领先的32位性能和同级领先的低功耗特性,其硅足迹显着小于业界同类产品。

P5600 CPU内核是为满足主流消费电子产品(包括连接的电视和机顶盒)所需的性能和功能而设计的,丰富而广泛的功能集将其适用性扩展到了从住宅网关到网络设备的各种网络应用程序中。 作为嵌入式应用程序中的高性能计算。

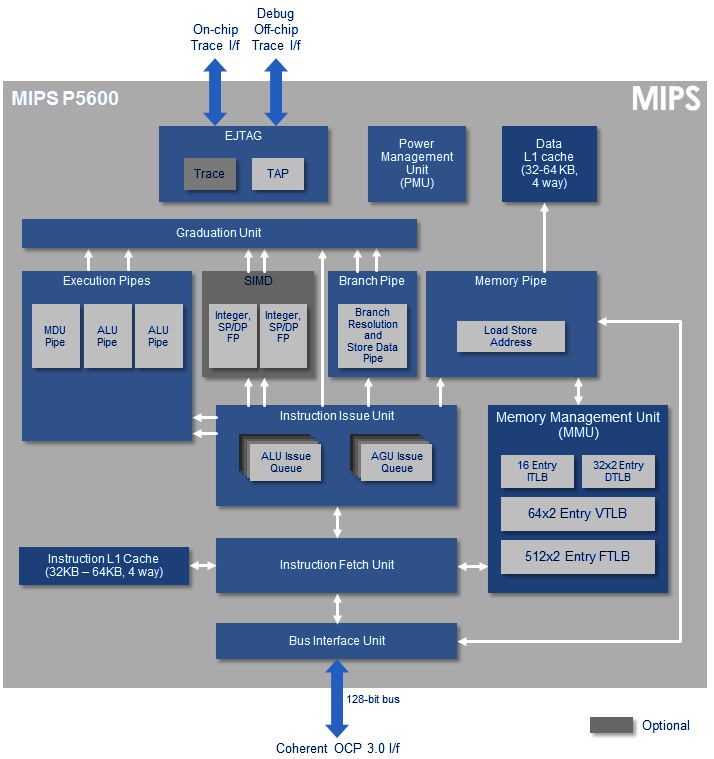

MIPS P5600 CPU基于MIPS32 架构的广泛问题,深度乱序操作(OoO)的实现,在具有高性能高速缓存一致性的单个群集中最多支持六个内核。作为其原始功能的补充,该内核还包括128位整数和浮点SIMD处理,硬件虚拟化以及物理和虚拟寻址功能增强。

MIPS P5600处理器IP内核是同类产品中最高效的CPU内核,可提供顶级性能,因此非常适合快速增长的互联消费电子市场中的各种应用。

P5600建立在现有proAptiv 系列微架构的基础上,增加了 128-bit SIMD, 带硬件表的硬件虚拟化,40位扩展物理寻址(XPA),以及在面向系统的软件工作负载上的性能显着提高。

P5600 CPU还达到了每个内核5.4 CoreMark / MHz和3.5 DMIPS / MHz,与其他高端CPU IP内核匹配或超过。

P5600处理器在性能上要比领先的IP内核替代产品小得多,在给定通用的工艺几何结构,相似的配置和合成技术的情况下,这些结果可将硅面积减小多达30%。SoC设计人员可以利用这种效率优势来节省大量成本和功耗,或者实现其他内核以提供与竞争性芯片相比的性能优势。

P5600 优势

• 复杂的分支预测,可在深度流水线CPU上最大化利用率和性能

• 加载/存储绑定以获得最佳数据移动性能

• 业界领先的基准测试和实际性能,其面积和功耗均低于竞争解决方案

• 128-bit SIMD - 加速指令的执行旨在以C,OpenCL等高级语言进行开发的指令集,从而加快了音频,视频,图形,图像,语音和其他面向DSP的软件算法的执行

• 基于硬件虚拟化的MIPS多域安全技术–确保需要安全的应用程序彼此有效,可靠地隔离,并免受非安全应用程序的攻击

• 增强型虚拟地址(EVA)和扩展物理地址(XPA)的高级寻址扩展

ºEVA支持3GB + Linux(和类似的OS)实施,而无需使用过度浪费的HIGHMEM

ºXPA将实体寻址扩展到1 TB(40位)

• 用于企业/消费者分区,安全内容访问,付款/交易以及将安全方案与众多内容源隔离的多上下文安全平台

• 广泛的软件和生态系统支持以及成熟的工具链

• 可用作可综合IP,可在带有标准单元和存储器的任何过程节点中实施

基本核心功能

• 32位MIPS32®版本5指令集架构

• 高性能,16阶段,广泛发射的乱序(OoO)管道

º每个周期可提取四指令

º每个周期三重绑定派发

º每周期4个整数和2个SIMD操作的指令峰值发射

º复杂的分支预测方案,再加上L0 / L1 / L2分支目标缓冲区(BTB),返回预测堆栈(RPS),跳转寄存器高速缓存(JRC)

º指令绑定–将两个32位整数访问合并为一个64位访问,或将两个64位浮点访问合并为一个128位访问,从而使内存密集型数据移动例程最多增加2倍

• 指令和数据的L1高速缓存大小分别为32KB或64KB,4路组关联

• 新的高性能双发射128位SIMD单元-可选

º32 x 128位寄存器组,向SIMD单元加载/从SIMD单元加载/存储128位

º本机数据类型:

• 8/16/32位整数和定点,16/32/64位浮点

º符合IEEE-754 2008

º通过CPU内核全速运行

• 全面的硬件虚拟化

º提供内核和用户空间的root和guest虚拟机特权级别

º支持多个来宾,每个来宾具有完整的虚拟CPU =来宾OS保持不变

º单独的TLB,root和guest虚拟机的COP0上下文–>完全隔离,快速上下文切换,由root处理异常和中断

ºTLB中的HW表格伴随支持可实现最佳性能

º完整的SoC虚拟化支持(IOMMU和中断处理–请参阅多核功能)

• 可编程内存管理单元 (MMU)

º增强型虚拟地址(EVA)-可编程内核和用户段大小

º扩展实体地址(XPA)–提供扩展到40位物理地址位(1 TB)

º第一级微型TLB(uTLB)– 16个输入指令TLB,32个输入数据TLB

º2级TLB –同时访问,可变和固定页面大小

º64x2入口VTLB,512x2入口4路组关联FTLB

º硬件表格伴随,可快速填充页面

• 电源管理功能

º多核集群电源控制器 (CPC):

• 基于寄存器,对操作系统可见/可控制

• 每个CPU电压域门控; 每个CPU时钟门控

• 集群级DVFS功能

º内核水平

• 整个内核的粗细和细粒度时钟门控

• 数据和指令L1缓存的路途预测

• 基于指令和寄存器的睡眠模式

• EJTAG / PDtrace调试块和接口

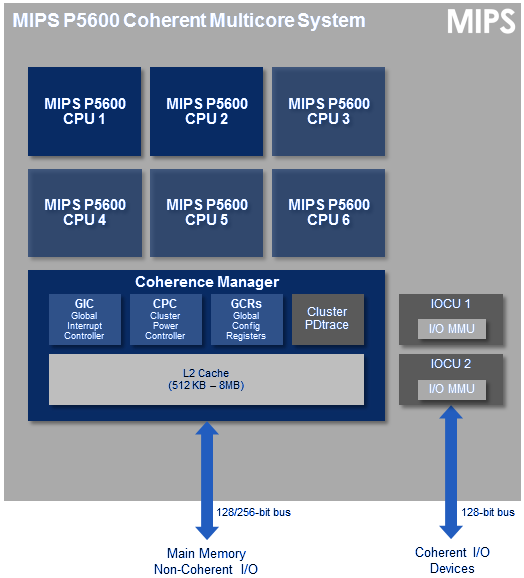

相干多核处理器功能

• 超标量,深度OoO多核处理器

• 完整的多核系统,旨在获得最大的群集级带宽

º一致性控制器 – 在一个集群中最多支持六个核心的多核心配置

º高带宽256位内部数据路径和外部系统接口

º集成的L2缓存(L2 $):4路集关联,最大8MB内存

• L2 $ RAM上的ECC选项可提供更高的数据可靠性

• 可配置的等待状态到RAM以实现最佳的L2 $设计

• L2 $硬件预取,可实现更高的吞吐量和性能

º每个相干处理系统最多两个IO相干单元(IOCU

º集群电源控制器(CPC),用于每个CPU的电压/时钟门控

º256中断全局中断控制器 (GIC)

º系统级别的虚拟化支持– IOCU具有IO MMU,而GIC具有虚拟化中断

• 先进的调试功能– PDtrace子系统允许查看核心和群集级别的跟踪信息

规格

| 频率 |

1 GHz - 2+ GHz* |

| CoreMark/MHz (每核) |

> 5 |

| Total CoreMark @ 1.5GHz |

> 7500 每核 |

| DMIPS/MHz (每核) |

3.5 |

| Total DMIPS @ 1.5GHz |

> 5250 每核 |

每个基本内核配置:注意:所示频率是基于预生产的P5600 RTL,并与全面规划双核proAptivimplementation的结果进行了比较,范围从最坏情况下的12T SVt面积优化的硅角,到12T MVt速度优化的典型角硅。 最终生产RTL结果可能会有所不同

• 具有奇偶校验,BIST的32KB Data / Inst L1高速缓存

• 新型高速整数+浮点(SP和DP)SIMD单元

• 功能齐全的MMU,使用多层TLB(I / D uTLB + 128个条目VTLB + 1024个条目FTLB)

• PDtrace™ 调试

多核集群配置:

• 每个以上具有两个完全配置的P5600内核

• Coherence Manager + 集成1MB L2 $ w / ECC

• 1个硬件IO一致性单元(IOCU)端口

• 集群级PDtrace

实施库/参数–基于以下方面进行了速度优化:

• 台积电28HPM 12T标准单元+ Synopsys存储器

• 数据量测是在最坏的操作条件情况slow-corner硅片(零温度,WCZ),OCV为10%,时钟抖动裕度为25ps,而非在typical硅片上