MIPS M6200/M6250 处理器内核是微控制器和嵌入式应用的理想选择。

M62xx内核是 MIPS microAptiv 系列的超集扩展,是第一个实施最新 MIPS 版本 6 架构 的M级处理器。

M6200和M6250实施6级流水线设计,并继续支持MIPS32和microMIPS ISA。

这些新的处理器内核继续提供M系列产品,在同一系列中提供了微控制器(MCU)和微处理器(MPU)版本:

M62xx系列包括以下处理器内核:

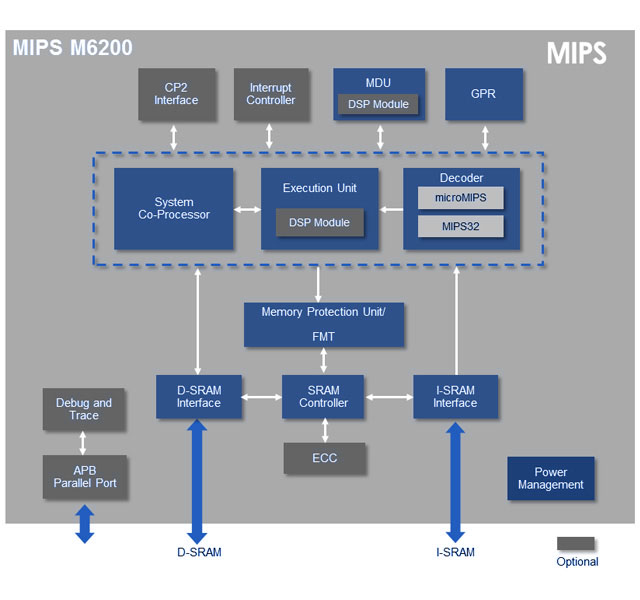

MIPS M6200

MIPS M6200 具有一个集成的64位SRAM控制器,一个存储器保护单元和一个实时,低延迟执行单元,针对低成本,低功耗的微控制器和嵌入式应用进行了优化。

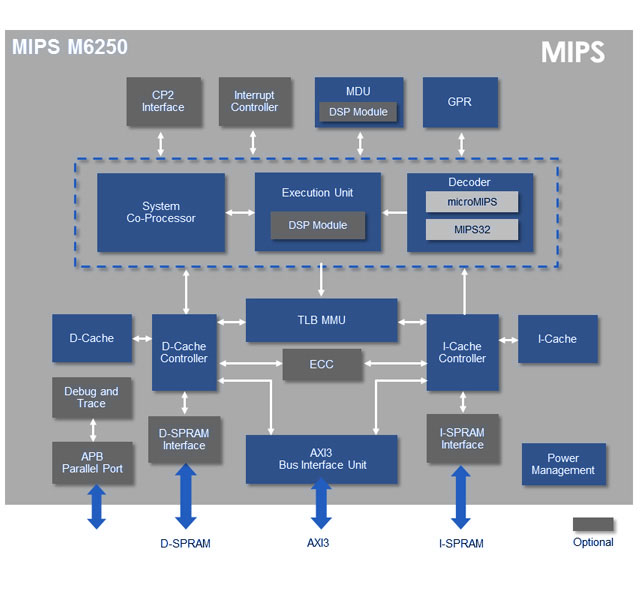

MIPS M6250

MIPS M6250 集成了高性能指令/数据L1高速缓存控制器和内存管理单元(MMU),可为高性能嵌入式应用程序执行Linux和其他丰富的操作系统。

M6200和M6250继续M级处理器的发展,提供了改进的性能和microAptiv内核的其他功能。 这些内核为要求高工作频率,增加整个存储空间,低功耗,小面积占用空间的数据完整性支持的广泛应用提供了引人注目的解决方案,其中包括:

• 物联网 (IoT) 和机器对机器(M2M)设备

• 高频网络,数据包检查/信息处理系统

• 大型位址空间嵌入式应用程序– SSD和闪存控制器,GPU协处理器

• 高可靠性的工业,企业和 汽车系统

• 穿戴式应用

下载

主要特点

• 等效MIPS microAptiv实施的频率提高30%

• 6 级流水线

º具有单周期ALU操作的加载/存储架构

• 专用 DSP 和SIMD模块

º单周期吞吐量的乘法和MAC操作

º支持32×32、16×16,双16×16,双8×8,双8×16

º实现超过150条指令,包括70条SIMD和38条乘法/ MAC指令

º支持多达4个累加器

• 32 个通用寄存器

º多达16个影子寄存器组

• 数据完整性:纠错(ECC)和奇偶校验

º指令和数据存储器的ECC支持:SPRAM,L1缓存和SPRAM

º单错误纠正和双错误检测 (SECDED)

º指令和数据的奇偶校验支持

• 高达4GB的虚拟内存支持–用户,内核和调试模式

• 调试端口

ºAMBA APB 并行调试端口

º支持混合核调试

• 调试和跟踪分析

º简单指令/数据断点支持– – 4I/2D, 8I/4D

º复杂指令/数据断点支持 – 8I/4D

º快速调试通道

º性能计数器和PC /地址采样分析支持

ºiFlowtrace指令跟踪

• 安全调试

• 电源管理

º集成了广泛的细粒度时钟门控

º通过寄存器控制或WAIT指令启动的掉电模式

• MCU 应用特定扩展 (MCU ASE)

º支持来自外部中断控制器的最多255个中断

º独立的优先级和向量生成

º自动中断处理指令

º支持尾链

º支持使用GPR替代集以减少中断延迟

• M6200内存管理单元 (MMU)

º多达16个区域的存储器保护单元,带有地址,大小和保护选项

º固定内存转换 (FMT)

• M6200: 紧密耦合的SRAM控制器

º单周期

º32位地址,64位数据

º双重指令和数据接口

• M6250 内存管理单元 (MMU)

º指令/数据转换后备缓冲区 (TLB)

º32 /双输入16全关联联合TLB (JTLB)

º4项指令TLB和4项数据TLB

• M6250: 40- 位扩展实体寻址

• M6250: AMBA 3 AXI 总线接口单元

• M6250: 可编程L1指令/数据缓存控制器

º最多64KB,2或4路关联

º64-字节缓存行大小

º64- 位指令/数据高速缓存,可在同一管线周期中访问

• M6250: 紧密耦合Sratchpad RAM(SPRAM)控制器 (可选)

º高达1MB的指令/数据SPRAM

• MIPS 调试中心(可选)

º支持与JTAG和/或APB兼容调试系统的连接

º支持多核调试

• 中断控制单元(可选)

º支持多达255个可配置中断

º支持中断源灵敏度(电平为正,电平为负,边沿为正,边沿为负,双边沿敏感)

| 28HPM 12T SVt |

M6200 |

M6250 |

| 频率 (MHz) |

750 | 750 |

| 内核面积 (mm2) |

0.19 | 0.23 |

| 内核功耗 (µW/MHz) |

60 | 62 |

启用DSP的16区内存保护单元 (M6200), 32个入口JTLB (M6250)

在slow corner,0.81V,0C,OCV,+ /-5%,25ps时钟抖动下测得的频率启用DSP的16区内存保护单元 (M6200), 32个入口JTLB (M6250)

核心区域已规划,已预先缩小

核心功率在0.9V,25C的typical corner测得

文件