MIPS M5150 / M5100处理器内核非常适合物联网,可穿戴设备以及其他嵌入式和实时应用。

M51xx内核是MIPS microAptiv,系列的超集扩展,具有:

• 五级流水线架构提供一流的性能

• microMIPS 指令集缩减代码尺寸

• MIPS DSP r2 模块

• 快速中断处理

• 先进的调试/分析功能

• 全面的电源管理

M51xx内核实现了合并了硬件虚拟化的MIPS Release 5架构。 虚拟化为MIPS多域安全性提供了基础,从而可实现任何嵌入式微控制器体系结构中最高的安全性。 虚拟化还为包括工业控制器,物联网(IoT),可穿戴设备,无线通信,汽车和存储设备在内的广泛应用增强了IP保护和可靠性。

为M51xx系列的M5100微控制器类和M5150嵌入式处理器版本提供了虚拟化支持,这是同类产品中没有的功能。

这些内核中的“防篡改”功能提供了额外的安全性,其中包括可以阻止对处理器进行不必要访问的对策。

可选的IEEE 754浮点单元可为单精度和双精度指令提供高性能支持。

M51xx系列包括以下处理器内核:

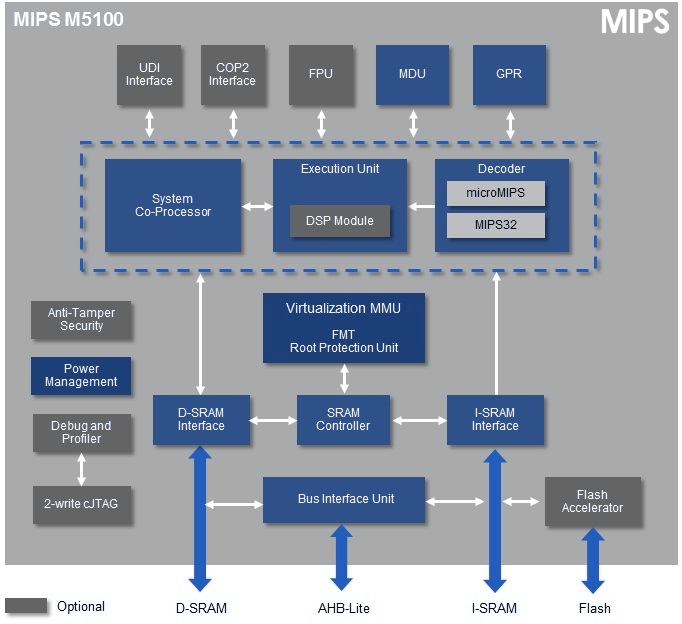

MIPS M5100

MIPS M5100 具有集成的SRAM控制器和实时执行单元,针对低成本,低功耗的微控制器应用进行了优化。

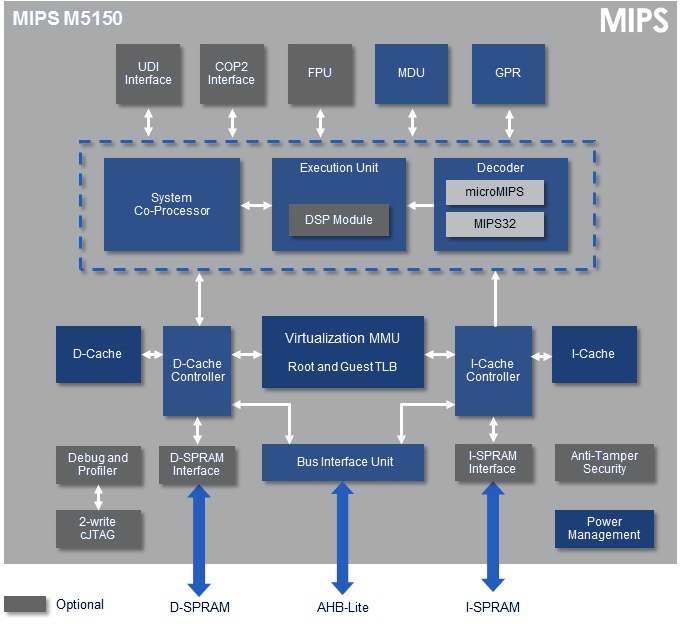

MIPS M5150

MIPS M5150 集成了高性能L1缓存控制器和虚拟内存管理支持,可用于高性能嵌入式系统应用程序和丰富的操作系统。

MIPS Series5 Warrior M级内核为各种嵌入式应用提供了高性能,可扩展且值得信赖的解决方案。

Warrior M系列CPU在M5100微控制器类(MCU)和M5150嵌入式处理器内核中提供了一流的性能和突破性的硬件虚拟化。

M51xx内核使各种系统都可以赢得低功耗,紧凑的面积尺寸等好处。并从高级别的安全性,可靠性和灵活性中受益。

M51xx内核是MIPS microAptiv系列的增强功能,采用相同的五级流水线架构设计,利用高性能数字信号处理(DSP)功能以及microMIPS ISA来减少代码大小

MIPS以及不断发展的合作伙伴生态系统提供了一套全面的硬件和软件开发工具,以提供支持。

MIPS和领先的第三方开发商(包括Seltech和巴西的PUCRS大学)已经提供并正在开发几种用于M级内核的管理程序。

应用领域

• 工业控制与自动化

• 物联网(IoT),机器对机器(M2M)

• 可穿戴

• 家用电器,数字消费产品

• 汽车行业

• 云计算

• 网络通讯

• 存储

优势

• 标准架构已在数百万SoC设计中得到验证

• 高性能,面积和能源效率高的架构:以比竞争对手更低的频率和更小的尺寸实现了性能要求

• 硬件虚拟化–支持独立,安全,高效且彼此完全隔离运行的多个软件环境

• 提供微控制器和嵌入式处理器版本,可在各种操作环境中使用

• 结合了MCU和DSP技术以进行具有成本效益的信号处理

• 灵活性和可扩展性–单一设计涵盖了广泛的应用

• FPU加速工业,汽车和数字消费类应用中的实时控制

• 广泛的软件和生态系统支持以及成熟的工具链

• 可用作可在任何过程节点中实现的可综合IP,带有标准单元和存储器

架构

• MIPS32版本5架构

• microMIPS 指令集架构

• 结合了16位和32位指令的增强代码压缩ISA

º支持所有现有的MIPS32指令; 添加新的16位和32位指令

º相对于仅32位的代码,最多可减少30%的代码大小

硬件虚拟化

• 创建彼此隔离,以内核特权级别运行的多个执行环境(来宾)

• 系统管理程序/安全监视器(根源)管理每个来宾的访问权限

º支持1型和2型管理程序

• 最多可支持7位来宾,每个来宾均提供唯一的ID; 来宾操作系统无需修改即可运行

• 7条新指令简化了“根源 到 客户”的沟通

• 支持多个内存管理单元选项,以实现最佳面积与功能

ºM5100 – FMT + 根源保护单元

ºM5150 – 访客TLB + 根源 TLB

ºM5150 – 访客TLB + 根源保护单元

• 允许来宾之间共享资源(内存,DSP,FPU等)

DSP r2模块

• 专用管道,与核心整数管道并行运行

• 实现超过150条指令,包括70条SIMD和38条乘法/ MAC指令

• 增强的乘法和除法单元

º单周期吞吐量乘法和MAC操作

º支持32×32、16×16,双16×16,双8×8,双8×16

• 支持多达4个累加器

浮点单元 (FPU)

• 单精度和双精度符合IEEE 754的FPU

• 支持IEEE-754 2008 Nan和ABS指令

• 专用的7级流水线,与核心整数流水线并行运行

• 大多数指令以1个周期的吞吐量和4个周期的延迟执行

• 执行1:1 Core:FPU时钟比率

• 同时支持MIPS32和microMIPS指令

防篡改

• 注入随机管道停顿

• 缓存/ SPRAM地址和数据加扰

• 2个伪随机数发生器,供用户软件和核心逻辑使用

内存控制器

• M5150 – L1高速缓存控制器,用于最大64KB的指令和数据大小,四路设置关联

• M5100 – 32位地址和数据SRAM接口,单独或统一的指令和数据接口

总线接口单元

• AMBA 3 AHB

EJTAG 调试和跟踪

• 安全调试功能–防止通过EJTAG端口流式传输指令

• 通过其他事件跟踪模式支持增强的iFlowtrace™

• 简单/复杂指令和数据断点支持– 2I / 1D,4I / 2D,6I / 2D,8I / 4D

• 支持2个具有多个事件类型选项的性能计数器

• 指令和数据地址采样:零虚耗,合格的读/写

• 支持2线cJTAG调试接口

电源管理

• 集成了广泛的细粒度时钟门控

• 实现由WAIT指令启动的掉电模式

可扩展性

• 可选的协处理器(COP2)和CorExtend™/用户定义的指令(UDI)接口

M5100 内核规格

| 优化**** |

速度 |

面积 |

速度 |

面积 |

| 频率* (MHz) |

322 | 100 | 497 | 100 |

| 效能 (DMIPS) |

505 | 157 | 780 | 157 |

| 面积 ** (mm2) |

0.77 | 0.2 | 0.23 | 0.04 |

| 内核运作功耗*** (mW/MHz) |

0.11 | 0.05 | 0.04 | 0.017 |

| 睡眠功耗 (µW/MHz) |

5.8 | 2.3 | 1.7 | 0.8 |

| 标准逻辑单元库 |

9T LVt | 9T SVt | 12T SVt | 9T LVt |

M5150 内核规格

| 优化 **** |

速度 |

速度 |

| 频率 * (MHz) |

372 | 576 |

| 效能 (DMIPS) |

584 | 904 |

| 面积 ** (mm2) |

0.89 | 0.26 |

| 内核运作功耗 *** (mW/MHz) |

0.13 | 0.07 |

| 睡眠功耗 (µW/MHz) |

2.7 | 1.5 |

| 标准逻辑单元库 |

9T LVt |

12T SVt |

注意:频率,功耗和尺寸取决于配置选项,综合,芯片供应商,工艺

* 生产频率 PTSI

65LP: +/- 5% OCV, 50ps 时钟抖动

28HPM: +/- 4% OCV, 25ps 时钟抖动

** 内核平面图区域

*** 在典型拐角处测得的功率, 25C at 1.2V/65LP, 0.9V/28HPM

**** M5100 速度优化 – microMIPS + FPU + DSP + 32KB/32KB I/D SRAM, FMT+32RPU + AHB

**** M5100 面积优化 – microMIPS + DSP +8RPU

面积优化频率可以高于/低于所选目标

**** M5150 速度优化 – microMIPS + FPU + DSP + 32KB/32KB I$/D$ + 32RTLB/32GTLB + AHB

与ARMv8-M CMSE相比的MIPS-VZ安全功能

下载说明:

ARMv8-M安全扩展(CMSE)基于信任区(TZ)。 与其他基于TZ的系统类似,有一个安全世界和一个非安全世界。 这意味着所有要保护的代码都必须彼此信任,因为它们都在同一共享的单个Secure World地址空间中执行。

MIPS-VZ基于硬件的CPU虚拟化,该虚拟化允许多个域,每个域彼此独立并相互保护。 这样做的好处是,每个要保护的软件都不必信任其他软件,因为每个软件都可以拥有一个私有域。 MIPS-VZ体系结构最多允许255个单独的域,而特定的CPU实现可能实现较少数量的域。